## UPPAAL

A Tool for Automatic Verification of Real-Time Systems

Johan Bengtsson and Fredrik Larsson

#### Abstract

As real-time systems often operate in safety-critical environments, it is extremely important to know that these systems are correct. A traditional way to guarantee the correctness of a real-time system is by simulation and testing. However, even if the system passes all imaginable tests, it does not guarantee that the system works correctly in all real life situations. This motivates the use of formal methods for modeling systems and verifying that they fulfill their specifications.

In this report we describe networks of timed automata as a formal model for real-time systems; we also describe how to extend this model to handle systems with drifting clocks. A simple logic for expressing safety properties of a system is presented, together with an algorithm for checking if a model satisfies a given property. We have implemented a tool, UPPAAL, for automatic verification, based on the algorithm and model mentioned above. To handle the infinite state-space UPPAAL uses constraint solving techniques to group states having the same properties. UPPAAL also adopts the on-the-fly verification techniques, to avoid constructing the parts of the state-space that are not reachable.

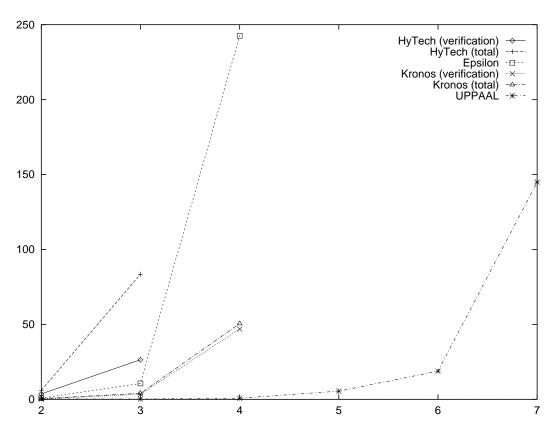

The performance of UPPAAL has been tested on various examples, including Fischers Protocol for mutual exclusion and Philips Audio Control Protocol. The performance of UPPAAL has also been compared to other verification tools, and the result shows that UPPAAL is not only faster, but also capable of dealing with larger systems.

## Acknowledgments

We want to thank Wang Yi (DoCS, Uppsala), Kim Larsen (BRICS, Aalborg) and Paul Petersson (DoCS, Uppsala) for help and guidance. We also want to thank the Department of Computer Systems at Uppsala University for a inspiring environment, and the Swedish Board for Technical Development (NUTEK) for the funding.

# Contents

| 1 | Introduction                         |                                             |    |  |  |  |  |  |

|---|--------------------------------------|---------------------------------------------|----|--|--|--|--|--|

| 2 | Modeling Real-time Systems           |                                             |    |  |  |  |  |  |

|   | 2.1                                  | Networks of Timed Automata                  | 3  |  |  |  |  |  |

|   | 2.2                                  | Networks of Linear Hybrid Automata          | 5  |  |  |  |  |  |

|   | 2.3                                  | Examples                                    | 5  |  |  |  |  |  |

|   |                                      | 2.3.1 Fischers Protocol                     | 5  |  |  |  |  |  |

|   |                                      | 2.3.2 Philips Audio Control Protocol        | 7  |  |  |  |  |  |

| 3 | $\mathbf{Ver}$                       | ifying Real-time Systems                    | 10 |  |  |  |  |  |

|   | 3.1                                  | Reachability Analysis by Constraint Solving | 10 |  |  |  |  |  |

|   | 3.2 Operations on Constraint Systems |                                             |    |  |  |  |  |  |

|   | Algorithms                           | 12                                          |    |  |  |  |  |  |

|   |                                      | 3.3.1 Forward Reachability Analysis         | 13 |  |  |  |  |  |

|   |                                      | 3.3.2 Backward Reachability Analysis        | 13 |  |  |  |  |  |

| 4 | UP                                   | PAAL                                        | 15 |  |  |  |  |  |

|   | 4.1                                  | Overview                                    | 15 |  |  |  |  |  |

|   | 4.2                                  | Functionality                               | 16 |  |  |  |  |  |

|   |                                      | 4.2.1 atg2ta                                | 16 |  |  |  |  |  |

|   |                                      | 4.2.2 hs2ta                                 | 16 |  |  |  |  |  |

|   |                                      | 4.2.3 checkta                               | 16 |  |  |  |  |  |

|   |     | 4.2.4   | verifyta                                         | 17 |

|---|-----|---------|--------------------------------------------------|----|

| 5 | Imp | olemen  | tation                                           | 18 |

|   | 5.1 | User I  | nterface                                         | 18 |

|   |     | 5.1.1   | Graphical interface                              | 18 |

|   |     | 5.1.2   | Textual Description Language                     | 19 |

|   |     | 5.1.3   | Property Description Language                    | 20 |

|   | 5.2 | The C   | Constraint Solvers                               | 21 |

|   |     | 5.2.1   | The Clock Constraint Solver                      | 21 |

|   |     | 5.2.2   | The Integer Constraint Solver                    | 35 |

|   | 5.3 | The V   | erifier                                          | 38 |

|   |     | 5.3.1   | Representation                                   | 38 |

|   |     | 5.3.2   | The Verification Algorithm                       | 39 |

|   |     | 5.3.3   | Finding Possible Transitions from a Global State | 40 |

|   |     | 5.3.4   | The Passed List                                  | 40 |

|   |     | 5.3.5   | The Principle of Maximum Delay                   | 42 |

|   |     | 5.3.6   | The Diagnostic Trace                             | 44 |

| 6 | Per | formai  | ace                                              | 46 |

|   | 6.1 | Fische  | rs Protocol Revisited                            | 46 |

|   | 6.2 | Philip  | s Audio Control Protocol Revisited               | 46 |

| 7 | Cor | nclusio | $\mathbf{n}\mathbf{s}$                           | 53 |

|   | 7.1 | Future  | e Work                                           | 53 |

|   |     | 7.1.1   | Other Constraint Solvers                         | 53 |

|   |     | 7.1.2   | Richer Logics                                    | 53 |

| A | UP  | PAAL    | User's Guide                                     | 55 |

|   | A 1 | Introd  | uetion                                           | 55 |

| A.2 | Hard- and software required by UPPAAL                            | 55 |

|-----|------------------------------------------------------------------|----|

| A.3 | How to describe Real-Time Systems                                | 56 |

|     | A.3.1 Networks of Timed Automata                                 | 56 |

|     | A.3.2 Networks of Linear Hybrid Automata                         | 60 |

|     | A.3.3 Syntax Checks                                              | 60 |

| A.4 | How to Specify Properties of Real-Time Systems                   | 60 |

| A.5 | Using the integrated environment                                 | 61 |

| A.A | Verification of a Simple System Using the Integrated Environment | 62 |

| A.B | Context Free Grammar for the Textual Format                      | 64 |

| A.C | Context Free Grammar for the Query Language                      | 64 |

## Chapter 1

## Introduction

The use of real-time systems becomes more and more common in our society nowadays. They are often embedded in safety-critical applications and it is therefore extremely important that they work correctly. One will also save money if errors can be detected as early as possible in the development process.

People who develop computer systems often use simulation techniques to "ensure" that the system works correctly. Simulation is the process when people interactively test how the system reacts in different situations on different inputs. But even if the system reacts satisfactory in these tests one will never know for sure that the system works correctly in all possible situations. This is why we need the verification phase in system development.

Verification can be thought of as a simulation of all possible inputs in all possible system states. It requires a formal way to model the system, a logic to express the properties and an algorithm that can verify if the model satisfies the properties expressed in the logic or not. For example if we have an automatic railway controller we want it to satisfy the property that not more than one train is allowed to cross the bridge simultaneously. This property is an example of a safety property of the system. Another thing one might want to assure is that a train will cross the bridge before a certain time. This is an example of a bounded liveness property.

If formal methods shall be useful it is important that they are powerful, easy to use and that there exist efficient programs doing the verification automatically. The user shall only be required to model the system, enter properties that he/she wants to check, press a button and after some time get information telling if, and maybe why, the properties were satisfied by the system model or not. However, one must remember that it is the model that is verified so; if the model does not correspond to the system the results are useless. Therefore modeling is also an important phase in system development. But in this report, we will mainly deal with automatic verification.

We have implemented a tool called UPPAAL that can be used to verify safety and bounded liveness properties of real-time systems modeled as networks of timed automata or linear hybrid automata<sup>1</sup>.

The implementation of UPPAAL has been done with the following things in mind:

• It should be as fast as possible.

$<sup>^{1}</sup>$  A linear hybrid automaton is an extension of the timed automaton, where the clocks may proceed with different rates.

- It must require as little memory as possible because the systems that one wants to verify can be large and complex.

- The design must be modular so that it's easy to reuse parts of the implementation and to add new types and features.

- Of course, it must also be easy to use.

These requirements are sometimes a bit contradictory. The choice of algorithms and data structures often forces one to do trade-offs between time and memory usage. General operations that are easy to reuse are not as fast as they could be if they were optimized by use of more problem specific details. The tool is implemented in C<sup>++</sup> using an object-oriented design. The implementation will be discussed in detail in a later chapter.

This report is organized in the following way:

Chapter 2 is about how to model real-time systems. It introduces timed automata as a formal model for real-time systems. There are also some examples that illustrate how the modeling works.

Chapter 3 is about the verification techniques implemented in UPPAAL. It describes the problem of reachability analysis and the verification algorithm based on constraint solving techniques.

Chapter 4 gives an overview of UPPAAL. It describes the functionality and structure of UPPAAL.

Chapter 5 describes in detail how UPPAAL is implemented. There will be proofs showing that used algorithms correspond to the semantic definitions of the operations mentioned in the algorithm description in chapter 3. It will describe the algorithms and data structures chosen and in some cases discuss alternative approaches and motivate why they weren't chosen.

Chapter 6 is about the performance of UPPAAL. It shows some examples that UPPAAL has been tested on and the time UPPAAL spent verifying them.

The last chapter of the report, chapter 7, contains concluding remarks.

Appendix A is the users guide to UPPAAL.

## Chapter 2

# Modeling Real-time Systems

We study real-time systems consisting of communicating processes with shared clocks. The systems are described by networks of timed automata [AD90] extended with auxiliary data variables and with a notion of parallel composition. Instead of interpreting parallel composition as logical conjunction (*i.e.* communication is only possible if all components in the system wants to communicate on the same channel) we use a CCS-like interpretation of parallel composition (proposed in [YPD94]), allowing one-to-one communication and interleaving.

## 2.1 Networks of Timed Automata

A timed automaton is a standard finite-state automaton extended with a finite collection of real valued clocks. The clocks are assumed to proceed at the same rate and their values may be compared with natural numbers or reset to 0. We have extended the notion of timed automata to include integer variables, *i.e.* integer valued variables that may be compared to natural numbers or assigned to any value of the form ax + b where  $a, b \in \mathbb{Z}$  and x is the variable being reassigned.

In our model we also allow clocks not only to be reset, but also to be set to any non-negative integer value.

**Definition 1** (Atomic Constraints) Let C be a set of real valued clocks and I a set of integer valued variables. An atomic clock constraint over C is a constraint of the form:  $x \sim n$ , for  $x \in C$ ,  $\sim \in \{\leq, \geq, =\}$  and  $n \in \mathbb{N}$ . An atomic integer constraint over I is a constraint of the form:  $i \sim n$ , for  $i \in I$ ,  $\sim \in \{\leq, \geq, =\}$  and  $n \in \mathbb{Z}$ .

Let  $C_c(C)$  denote the set of all clock constraints over C, and let  $C_i(I)$  denote the set of all integer constraints over I.

**Definition 2** (Guards) Let C be a set of real valued clocks and I a set of integer valued variables. A guard g over C and I is a formula generated by the following syntax:  $g := c \mid g \land g$ , where  $c \in (\mathcal{C}_{\mathcal{C}}(C) \cup \mathcal{C}_{i}(I))$

We let  $\mathcal{B}(C, I)$  stand for the set of all guards over C and I.

**Definition 3** (Assignments) Let C be a set of real valued clocks and I a set of integer valued variables. A clock assign over C is a tuple  $\langle v, c \rangle$ , where  $v \in C$  and  $c \in \mathbb{N}$ . An integer assign over I is a tuple  $\langle v, c_1, c_2 \rangle$  representing the assignment  $v = c_1 \cdot v + c_2$ , where  $v \in I$  and  $c_1, c_2 \in \mathbb{Z}$ .  $\square$

We will use  $\mathcal{A}(C,I)$  to denote the power-set of all assignments over I and C.

**Definition 4** (Timed Automaton) A timed automaton A over a finite set of actions Act, clocks C and integer variables I is a tuple  $(L, l_0, E)$ , where L is a finite set of nodes (control-nodes),  $l_0$ is the initial node, and  $E \subseteq L \times \mathcal{B}(C, I) \times Act \times \mathcal{A}(C, I) \times L$  corresponds to the set of edges. To denote,  $\langle l, g, a, r, l' \rangle \in E$ , we will write  $l \xrightarrow{g,a,r} l'$ .

In order to study compositionality problems we introduce a parallel composition between timed automata. In order to get the kind of parallel composition we want, we have to introduce the notion of co-actions, that is done by defining a synchronization function  $\mathcal{T}$ .

**Definition 5** (Synchronization Function) Let  $\mathcal{T} \subseteq Act \times Act$  be a function such that:

$$\langle a_i, a_j \rangle \in \mathcal{T} \Rightarrow \langle a_j, a_i \rangle \in \mathcal{T}$$

for all  $a_i, a_j$

**Definition 6** (Parallel Composition) Let  $A_1, A_2$  be two timed automata. Then the parallel composition  $(A_1|A_2)$  is a timed automaton  $\langle L, l_0, E \rangle$ , where  $(l_1|l_2) \in L$  whenever  $l_1 \in L_1$  and  $l_2 \in L_2$ ,  $l_0 = (l_{1,0}|l_{2,0})$ . The edges E are defined as follows:

$\begin{array}{ll} \bullet & (l_1|l_2) \xrightarrow{g,\tau,r} (l_1'|l_2') & \text{if } (l_1\xrightarrow{g_1,a_1,r_1} l_1') \wedge (l_2 \xrightarrow{g_2,a_2,r_2} l_2') \wedge (g=g_1 \cup g_2) \wedge (\langle a_1,a_2 \rangle \in \mathcal{T}) \wedge (r=r_1 \cup r_2) \\ \bullet & (l_1|l_2) \xrightarrow{g,a,r} (l_1'|l_2) & \text{if } l_1\xrightarrow{g,a,r} l_2' \\ \bullet & (l_1|l_2) \xrightarrow{g,a,r} (l_1|l_2') & \text{if } l_2\xrightarrow{g,a,r} l_2' \end{array}$

Note that parallel composition is commutative and associative.

A state of a timed automaton A is a pair (l, u) where l is a node of A and u is an assignment, mapping each clock in C to a value in  $\mathbb{R}^+$ , and each integer variable in I to a value in  $\mathbb{Z}$ . We will use g(n) to denote that the assignment u satisfies the guard g. The initial state of A is  $\langle l_0, u_0 \rangle$ , where  $u_0$  is the assignment mapping all variables to 0.

An automaton may take two types of transitions, from state to state:

- Delay transition:  $\langle l, u \rangle \stackrel{\epsilon(d)}{\leadsto} \langle l, u' \rangle$  following the rules given in definition 7

- Action transition:  $\langle l, u \rangle \stackrel{g,a,r}{\leadsto} \langle l', u' \rangle$  following the rules given in definition 8

**Definition 7** (Delay transition) Let  $\langle l, u \rangle$  and  $\langle l', u' \rangle$  be two states of a timed automaton A, and let d be a positive real. Then

$$\langle l, u \rangle \stackrel{\epsilon(d)}{\leadsto} \langle l', u' \rangle iff$$

$$\begin{cases} l' = l \\ u'(x) = u(x) + d & \text{if } x \in C \\ u'(x) = u(x) & \text{if } x \in I \\ d \leq M(l, u) \end{cases}$$

Where M(l, u) is the maximal delay of  $\langle l, u \rangle$ , defined as follows:

$$M(l,u) = \begin{cases} \sup\{t \mid g(u+t)\} & \text{if } \exists \ l' : l \xrightarrow{g,a,r} l' \\ \infty & \text{otherwise} \end{cases}$$

Intuitively this means that an automaton may not stay in a control-state long enough for the last outgoing edge from that state to close. This results in a maximal progress behavior of the automaton.

**Definition 8** (Action Transition) Let  $\langle l, u \rangle$  and  $\langle l', u' \rangle$  be two states of a timed automaton A. Then

$$\langle l, u \rangle \stackrel{g,a,r}{\leadsto} \langle l', u' \rangle \text{iff } (l \xrightarrow{g,a,r} l') \land g(u) \land \left( u'(x) = \begin{cases} c_0 & \text{if } x \in C \land \langle x, c_0 \rangle \in r \\ c_1 u(x) + c_0 & \text{if } x \in I \land \langle x, c_1, c_0 \rangle \in r \\ u(x) & \text{otherwise} \end{cases} \right)$$

## 2.2 Networks of Linear Hybrid Automata

The model of timed automata can be extended by allowing the clocks to proceed with different rates, and also allowing the rates to drift within a bounded interval. This model is often refered to as linear hybrid automata.

It has been shown in [AOY94] that for a restricted subclass of linear hybrid automata, each linear hybrid automaton can be simulated by a timed automaton. The restrictions nedded are:

- The clocks must never be stoped, i.e. it must never be possible for a clock to have rate 0.

- If we have an edge e between two nodes l and l', any clock which rate in l' differs from the rate in l must be reset on e.

- Any clock with negative rate must have a finite upper bound in each node, and any clock with positive rate must have a finite lower bound in each node.

## 2.3 Examples

## 2.3.1 Fischers Protocol

The protocol was proposed by Fischer and described by Lamport [Lam87]. Its purpose is to guarantee mutual exclusion in a concurrent system consisting of several processes using a variable shared among the processes and properly timing the processes in changing the shared variable. Each of the processes is assumed to have a local clock. The idea behind the protocol is that the timing constraints on the local clocks are set so that only one process can change the global variable to its own process number, then read the global variable later and if the shared variable is still equal to its own number, enter the critical section.

We will study two versions of the protocol, one simplified version allowing only one process to enter the critical section and never exit it, and one more advanced version with cyclic processes.

We start with a simplified version of the original protocol. It permits only one process to enter its critical section, and that process will then stay in the critical section forever. Recovery from failure to enter the critical section is omitted. This version of the protocol has been thoroughly studied by researchers e.g. [AL93, Sha93, YPD94].

Assume a concurrent system with n processes  $P_1 \dots P_n$ . We use a global clock  $x_i$  to model the local clock of process  $P_i$ . A process  $P_i$  may be in either of four local states A,B,C or Cs. Initially all processes are in their A-state and the shared variable id is 0.

A process  $P_i$  that wants to enter the critical section can try to do so if id = 0. Then it changes its local state from A to B. In state B it can only stay for less than T time-units before it proceeds to state C. When proceeding from state B to state C the process changes the value of id to it's own process number (i.e. id := i). In state C the process has to wait for, at least, T time-units. Then, before proceeding it must check that the shared variable id still has the value i. If it does, then  $P_i$  can proceed to Cs.

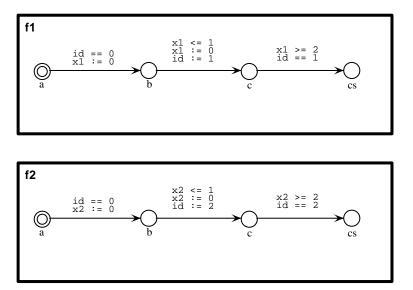

A graphical modeling of the simplified version of Fischers protocol, with two processes and T = 1, is shown in figure 2.1.

Figure 2.1: A simplified version of Fischers mutual exclusion protocol, with two processes.

Now we extend the protocol to cyclic processes. Each process may stay in the critical section for an unbounded amount of time each cycle, and recover from failure to enter the critical section.

As in the simple case we assume a concurrent system with n processes  $P_1 \dots P_n$ , and we use n global clocks  $\mathbf{x}_1 \dots \mathbf{x}_n$  to model the local clocks of the processes.

Also as in the simple case, when a process wants to enter the critical section, it can try to get access only if a shared variable id is 0. If it is, the process can proceed to a new state, B. In the new state it can only stay for less than T time-units before it has to proceed to state C. When proceeding from state C the process changes the value of C to it's own process-ID. In state C the process has to wait for, at least C time-units. If C to still contains the process-ID of this process, it can enter the critical section, otherwise it must restart the entering procedure, from

the beginning. After leaving the critical section, the process just resets the value of id to 0 and start over.

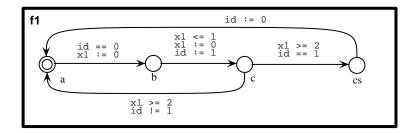

A graphical model of a system with two processes is shown in figure 2.2.

Figure 2.2: Fischers mutual exclusion protocol, with two cyclic processes.

## 2.3.2 Philips Audio Control Protocol

This is an example from a real-world application, and it was first described and verified by Bosscher et. al. [BPV93].

The example is a simplified version of an audio control protocol developed by Philips for the physical layer of an interface bus, that connects the various parts of stereo equipment. The protocol uses Manchester encoding, and it has to deal with uncertainty in the timing of the events, due to both hardware and software constraints.

## Description of the Protocol

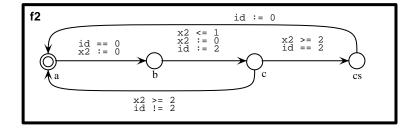

The protocol uses the well-known Manchester encoding of bit strings. In this encoding it is assumed that the time axis is divided into time-slots of equal length and each one is capable of transmitting one bit of data. In the message sent over the bus, a "1" is represented by an up going edge in the middle of a time-slot and a "0" is represented by a down going edge in the middle of a time-slot. If two bits with the same value are sent in a row, an additional edge is placed in between the two time-slots. An example of the encoding is shown in figure 2.3.

In addition to clock drift of up to 5% between the different parts of the system, the protocol has to face a number of other difficulties:

1. Although the receiver knows the length of the time-slots, it does not know when the first slot begins. This problem is resolved by requiring that the first bit sent is always a "1".

Figure 2.3: Manchester encoding of 1001

- 2. A receiver does not know the length of the message it is receiving.

- 3. In reality, the signal on the bus is not perfectly block-shaped. In particular, the time it takes for the bus to change from high to low make it impossible for the receiver to reliably detect a down going edge, and for this reason the receiver has to decode the message without seeing the down going edges. This is always possible, except that a message ending with "10" cannot be distinguished from the same message ending with "1". To solve this problem, we require that the messages always end with "00" or have an odd number of bits

- 4. Different senders may start sending at the same time; so bus collisions may occur.

- 5. The message delay in the bus can be significant.

For simplicity, all complications that arise from problems 4 and 5 are ignored. We assume a setting where one sender, and one receiver are communicating through a bus with negligible delay.

### Modeling the Protocol

In modeling the protocol, we adopt the method described by Ho and Wong-Toi [HWT95]. The protocol is divided into four processes:

- 1. An input-process that nondeterministically generates valid messages, starting with a "1" and ending either after an odd number of bits, or with "00". To achieve this, we use an integer valued variable k as a "parity-counter", i.e. k is one if an odd number of bits have been generated, and 0 if an even number of bits have been generated.

- Each time the sender consumes a bit, the value of the next bit is chosen. At this point the process may also end the message. The input-process gives the sender-process opportunity to check the value of the next bit to be sent, using three different channels: head\_1 for checking if next bit is "1", head\_0 to check if next bit is "0", and head\_e to check if the message has ended.

- 2. A sender-process that generates Manchester encoded signals by looking at the next bit, and determine the time for the next voltage change. It uses the channel up to signal an up going edge. A down going edge is not signaled at all, to model that the down going edges can't be detected.

- 3. A receiver-process that decodes the incoming message by measuring the times between the up signals. If no new up signal arrives in due time, we assume that the transmission has ended. We use an integer valued "length parity counter", m, as well as the four channels; output\_0, output\_1, output\_neq\_0, and output\_neq\_1, for error detection.

4. An output-process that checks if the bit received by the receiver is the expected bit, and signals the result using one of the four channels output\_0, output\_1, output\_neq\_0, or output\_neq\_1.

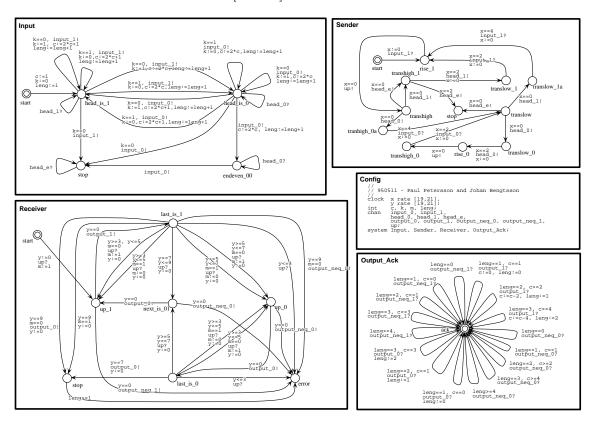

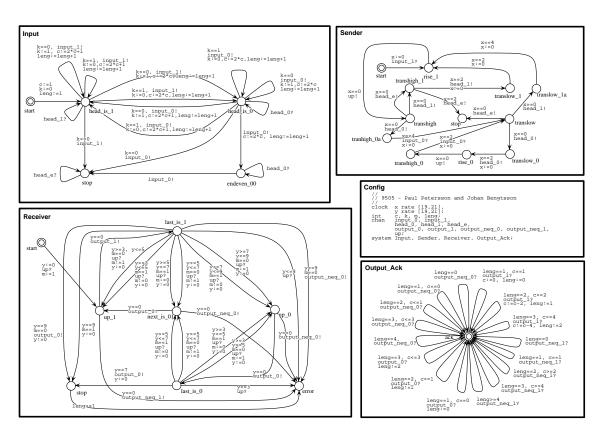

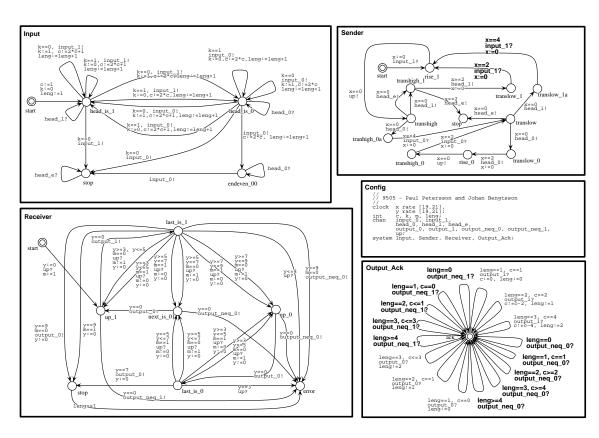

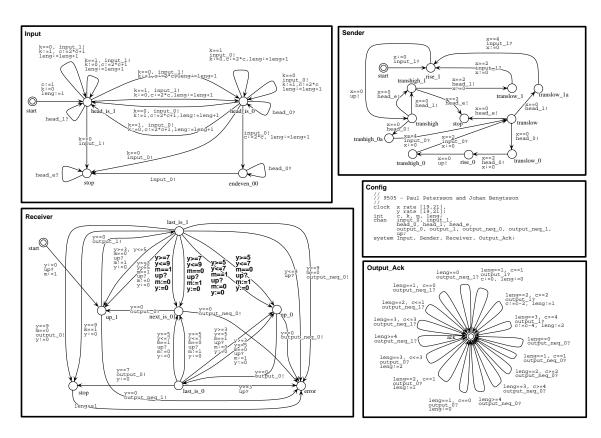

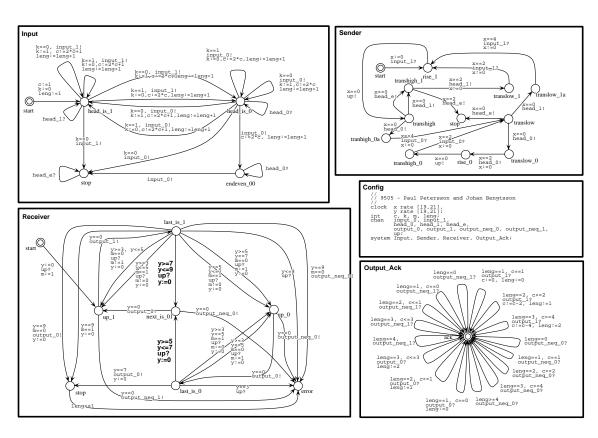

A graphical description of our model of the protocol can be seen in figure 2.4. The description is given as a linear hybrid-system, *i.e.* a system where the rate of clocks may vary, in a bounded interval. Those kind of systems can be modeled in the same way as timed automata, and they can be transformed into timed automata [AOY94].

Figure 2.4: Audio Control Protocol

## Chapter 3

# Verifying Real-time Systems

As mentioned earlier, the increasing use of real-time systems makes it important to develop methods for verifying that the systems behave correctly. In particular, as many of the real-time systems today are embedded in safety-critical environments, where the consequences of a system failure could cause a disaster.

It has been pointed out in [Hal93, YPD94], that the practical goal of verification of real-time systems, is to verify simple safety properties *i.e.* properties of the type "can we guarantee that a bad thing won't occur?" or "are we sure that eventually a good thing will occur?". Properties usually formalized in temporal logic as  $\forall \Box \neg bad$ -thing and  $\exists \Diamond good$ -thing For traditional finite-state systems this kind of properties can be verified by checking all possible reachable states of a system. Unfortunately the systems considered here are infinite-state because of the real-valued clocks.

## 3.1 Reachability Analysis by Constraint Solving

Adopting the methodology developed in [YPD94], we start with describing a simple reachability problem for timed automata. A generalized version of the problem will be given later.

**Definition 9** (Simple Reachability) Let  $\langle l_0, u_0 \rangle$  and  $\langle l_f, u_f \rangle$  be states of a timed automaton A. Then  $\langle l_f, u_f \rangle$  is reachable from  $\langle l_0, u_0 \rangle$  iff there exists a trace  $\langle l_0, u_0 \rangle \stackrel{Q_1}{\leadsto} \cdots \stackrel{Q_n}{\leadsto} \langle l_f, u_f \rangle$  that leads to the final state.

Note that the simple reachability relation is the transitive and reflexive closure of the transition relation.

To solve the problem with infinte state–space we use constraint systems to symoblically represent sets of assignments that we call time regions.

**Definition 10** (General Reachability) Let  $l_0, l_f$  be nodes of a timed automaton A, and let  $U_0, U_f$  be sets of assignments. We say that  $\langle l_f, U_f \rangle$  is reachable from  $\langle l_0, U_0 \rangle$  iff there exists  $u_0 \in U_0$  and  $u_f \in U_f$  such that  $\langle l_f, u_f \rangle$  is reachable from  $\langle l_0, u_0 \rangle$ .

We will now describe an algorithm for solving the general reachability problem, using constraint-solving techniques.

Let A be the timed automaton to be analyzed. We assume that the clocks of A can be ordered as a vector  $\langle c_1, c_2, \ldots, c_n \rangle$ . Then the clock part of an assignment can be seen as a point in the n-dimensional space  $\mathbf{R}^n_+$ . We will use linear constraint systems to describe regions of such points, and solve the general reachability problem by manipulating such linear constraint systems.

## A Class of Simple Linear Constraint Systems

The class of constraints we will study will always take the form:  $l_i \leq x_i \leq u_i$  or  $l_{ij} \leq x_i - x_j \leq u_{ij}$ . We will use the term *linear constraint system* to denote a set of constraints of that form. A solution to a linear constraint system r is an assignment that maps each variable to a value that satisfies the constraints.

The solution set of a constraint system r (i.e. the set of all solutions to r.) can be seen as a convex polytope in the n-dimensional space.

From now on we will simply call a constraint system r a region, referring to its solution set. We will use  $r = \emptyset$  to denote that r is not satisfiable, (i.e. its solution set is empty),  $r \subseteq r'$  to denote that r implies r' and  $r \wedge r'$  to denote the intersection of the solution sets of r and r'.

To represent a constraint system, we introduce a particular clock  $x_0$  which always has value 0. Then we may assume that all constraints in the system have the form  $l_{ij} \leq x_i - x_j \leq u_{ij}$ . Constraint systems on this form can easily be represented by matrices.

## 3.2 Operations on Constraint Systems

The subject of this section is to describe an algorithm that decides if a symbolic state  $\langle l_f, U_f \rangle$  is reachable from a symbolic state  $\langle l_0, U_0 \rangle$ .

The algorithm will manipulate r by use of constraint solving. The guards and resets on the transitions and delays in the state are the things that affect the constraints and motivate the operations introduced. The direction of the reachability analysis, forward or backward, will need different operations on constraint systems.

#### **Definition 11** (the delay operations)

1. The weakest precondition of a time region r is defined as

$$wp(r) = \{x \mid \exists d \ge 0 : x + d \in r\}$$

2. The strongest postcondition of a time region ris defined as

$$sp(r) = \{x \mid \exists d \ge 0 : x - d \in r\}$$

This operations are needed because the automaton may delay in a state, perform delay transitions, before an action transition is performed. If the reachability analysis is forward we start from  $\langle l_0, U_0 \rangle$  and search forward for  $\langle l_f, U_f \rangle$ . In this case the strongest postcondition is used. If we do backward reachability analysis we search backward from  $\langle l_f, U_f \rangle$  to  $\langle l_0, U_0 \rangle$  and handle delays with weakest precondition.

**Definition 12** (guard conjunction) If r is a time region and g is a set of guards the time region after the guard conjunction is the intersection of the solution sets:  $g \cap r$

This operation is performed when determining which transitions are enabled or not. If r' becomes inconsistent we have  $r' = \emptyset$ .

**Definition 13** (operations treating resets) Let r be a time region and k the clock to be reset.

1. reset(r, k) is defined as

$$\{v \mid \exists w \in r : v_k = 0 \land \forall i \neq k : v_i = w_i\}$$

2. free(r, k) is defined as

$$\{v \mid \exists w \in r \ : \ v_k \in \mathbf{R} \land \forall i \neq k \ : \ v_i = w_i$$

3. The Boolean operation check(r, k) is defined as

$$\{v \mid v \in r \land v_k = 0\} \neq \emptyset$$

The reset operation is used in forward reachability analysis to handle the resets that may be performed when the system perform a transition. In backward reachability analysis the free and check operations are used to handle the resets on the transitions. It is straight forward to extend the above definition to handle sets of resets and resets involving other values than 0.

The implementation of the algorithm and operations are much easier if the time regions are of a special form called closed.

**Definition 14** Let r be a time region of the form  $x_i - x_j \le u_{i,j}, x_0 = 0$ . r is closed if it satisfies

$$\forall d_{i,j} \leq u_{i,j} \exists x_i \exists x_j : x_i - x_j = d_{i,j}$$

Time regions are closed under the operations defined above.

## 3.3 Algorithms

We're now in a position to present an algorithm performing reachability analysis using constraint solving. The algorithm checks if a state in a timed automaton is reachable from the initial state or not.

When searching the state space we need two buffers that we can call wait and passed respectively. The wait buffer holds the states not yet explored and the passed buffer holds the states explored so far. We will treat the forward and backward reachability analysis algorithms in separate subsections.

## 3.3.1 Forward Reachability Analysis

If we do forward reachability analysis we initially store  $\langle l_0, U_0 \rangle$  in the wait buffer. We then repeat the following:

**Algorithm 1** 1. Pick a state  $\langle l_i, U_i \rangle$  from the wait buffer.

- 2. Check if  $l_i = l_f \wedge U_i \subseteq U_f$ . If that is the case, return the answer yes.

- 3. If  $l_i = l_j \wedge U_i \subseteq U_j$ , for some  $\langle l_j, U_j \rangle$  in the passed buffer, drop  $\langle l_i, U_i \rangle$  and go to step 1. Otherwise save  $\langle l_i, U_i \rangle$  in the passed buffer. If  $U_j \subset U_i$  we can replace the state  $\langle l_j, U_j \rangle$  with  $\langle l_i, U_i \rangle$ . (To save space)

- 4. Find all  $l_k$  that are reachable from  $l_i$  in one step regardless of the assignments, taking only actions into account. Let  $g_k$  be the set of guards on the performed transition and  $a_k$  the set of resets.

- 5. Now set  $U_k = reset(sp(U_i) \cap g_k, a_k)$ . If  $U_k \neq \emptyset$ , store  $\langle l_k, U_k \rangle$  in the wait buffer.

- 6. If the wait buffer is not empty go to step 1, otherwise return the answer no.

## 3.3.2 Backward Reachability Analysis

To simplify the algorithm description below we define an operation  $inv\_reset$  which entirely is composed of operations defined above.

**Definition 15** Let r be a time region and a set of resets. We define

$$inv\_reset(r,a) = \left\{ \begin{array}{cc} free(r,a) & check(r,a) \\ \emptyset & otherwise \end{array} \right.$$

If we do backward reachability analysis we initially store  $\langle l_f, U_f \rangle$  in the wait buffer. We then repeat the following:

**Algorithm 2** 1. Pick a state  $\langle l_i, U_i \rangle$  from the wait buffer.

- 2. Check if  $l_i = l_0 \wedge U_0 \subseteq U_i$ . If that is the case, return the answer yes.

- 3. If  $l_i = l_j \wedge U_i \subseteq U_j$ , for some  $\langle l_j, U_j \rangle$  in the passed buffer, drop  $\langle l_i, U_i \rangle$  and go to step 1. Otherwise save  $\langle l_i, U_i \rangle$  in the passed buffer. If  $U_j \subset U_i$  we can replace the state  $\langle l_j, U_j \rangle$  with  $\langle l_i, U_i \rangle$ .

- 4. Find all  $l_k$  that leads to  $l_i$  in one step regardless of the assignments, taking only actions into account. Let  $g_k$  be the set of guards on the performed transition and  $a_k$  the set of resets.

- 5. Now set  $U_k = inv\_reset(wp(U_i) \cap g_k, a_k)$ . If  $U_k \neq \emptyset$  store  $\langle l_k, U_k \rangle$  in the wait buffer.

- 6. If the wait buffer is not empty go to step 1, otherwise return the answer no.

Everything treated in this section will be discussed in greater detail later, when the implementation is described.

## Chapter 4

## **UPPAAL**

## 4.1 Overview

UPPAAL is a set of tools for automatic verification of safety and bounded liveness properties of real-time systems, modeled as networks of timed automata or simple linear hybrid systems<sup>1</sup>. The toolkit is implemented in C and C<sup>++</sup>, and it runs on several different types of UNIX-systems, including SunOS, Linux and HP-UX.

The functions of the toolkit are implemented in terms of modules. To simplify the connection of modules there are some shell-scripts, e.g. atg2hs2ta (connecting atg2ta and hs2ta). There is also a shell-script working as an integrated environment for verification.

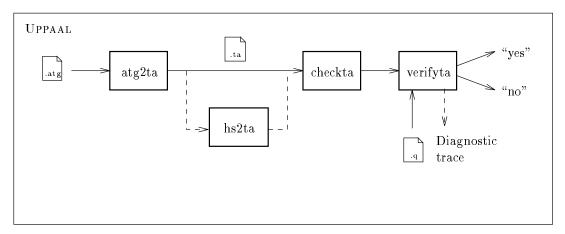

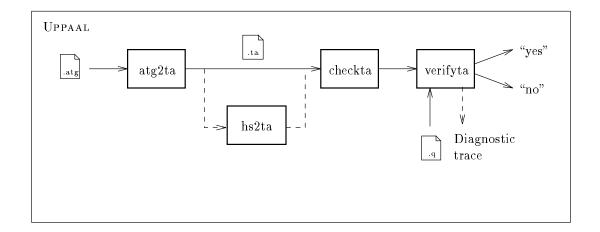

The basic structure of the toolkit is shown in figure 4.1.

Figure 4.1: An overview of UPPAAL

$<sup>^1</sup>$  UPPAAL is capable of transforming some simple classes of linear hybrid systems into timed automata.

## 4.2 Functionality

## 4.2.1 atg2ta

The atg2ta program is responsible for transforming graphical descriptions in Autograph to the textual format. In drawing the graphical description the following rules should be followed:

- The different processes of a system must be enclosed in boxes, with the name of the process as a structural label.

- All states in each process must have a name associated. The name can be given in any visible label assigned to the state. The state names of a process are local, and can be reused in other processes.

- All transitions must be between states in the same process. Transitions between processes

are not allowed.

- Conditions on the transitions can be given in any visible label for that transition.

- There must be a box describing the system configuration. It is a box with the word "config" as structural label, and declarations of the variables and system configuration, in the behavioral label. The declarations and system configuration should be given on the form described in the textual description format.

- A box containing no states, and without "config" as structural label, is considered as a comment, and is ignored by the translation program.

During the conversion atg2ta does only minimal syntax checks, to allow both timed automata and hybrid systems to be described using basically the same graphical syntax.

### 4.2.2 hs2ta

This program is capable of transforming simple linear hybrid systems into networks of timed automata. The systems handled belong to a subclass of  $LHS_{\neq 0}$ , where the rates of the hybrid variables are independent of the state of the system, a class of system sometimes referred to as multirate automata. The transformation is performed using an algorithm described by Sifakis *et. al.* [AOY94].

### 4.2.3 checkta

The checkta program is a program for checking the syntax of a description given in the textual format. The description to check must be a timed automaton, if it is a hybrid system, it must first be transformed using hs2ta.

The errors caught by checkta are, except for structural errors that violates the grammar<sup>2</sup>:

<sup>&</sup>lt;sup>2</sup>A context free grammar over the textual description format is shown in table 5.1

- That all datatypes used are supported. (Today, the only supported datatypes are clocks and integers.)

- That all variables and channels are declared.

- That the processes have unique names.

- That all states in the processes are declared, and that all processes have an initial state.

- That both source and destination of the transitions are states, and that the states are declared in the same process as the transition. Note that state declarations are local to the process, so the same state name can be reused in other processes.

- That the guard and assign labels on the transitions are well formed.

- That only declared processes are used in the system.

## 4.2.4 verifyta

The program **verifyta** is the verification engine of the UPPAAL toolkit. It takes a description and a property, and gives "yes" or "no" as an answer. As an option, it is also capable of showing an example trace that violates, or confirms the property.

The verification is performed in a backwards manner, *i.e.* the verifier starts in a symbolic state of the system, that satisfies the property (or its negation), and tries to find its way back to the initial state. The choice of states to start the verification in, is determined by the structure of the property. If the property is of the type  $\exists \Diamond P$  then the symbolic states satisfying the property are chosen as start states, and if we find a way back to the initial state the property is satisfied. If we, on the other hand, have a property of the type  $\forall \Box P$  we start in the symbolic states satisfying the negation of the property, and if we find a way back to the initial state, we know that the property is violated.

## Chapter 5

# Implementation

## 5.1 User Interface

## 5.1.1 Graphical interface

The graphical interface is implemented based on Autograph<sup>1</sup>.

Autograph is capable of saving the drawn automata, in three different formats; fc2-format, atg-format, and postscript-format. Since the fc2-format is to limited for us to use, and the postscript-format is far to complex, we use the atg-format.

Given a file on atg-format, a part of the tool extracts all vital information, and translates it into our own textual description language. In the translation procedure, we do not pay attention to syntactical errors. This is to simplify the translation part, and to allow further extensions to the graphical "language".

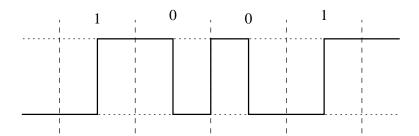

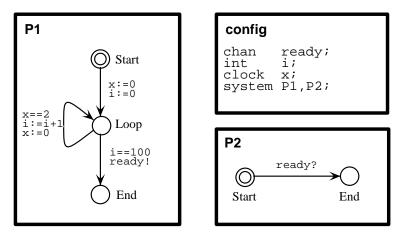

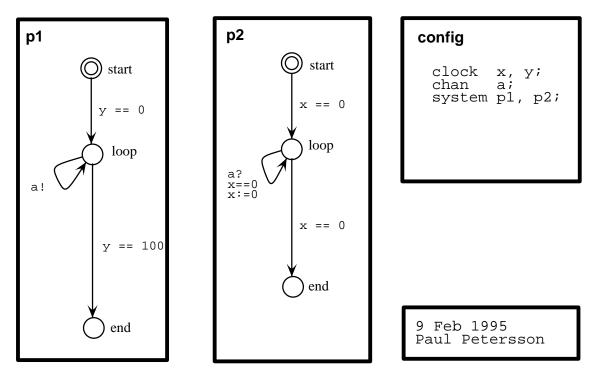

An example of a system described in the graphical format is shown in figure 5.1

Figure 5.1: An example of a system described in the graphical format.

<sup>&</sup>lt;sup>1</sup> Autograph is a tool for drawing automata, developed at CMA, France.

```

VarList ProcList Globals

Ita

VarList

\epsilon \mid Channel\ VarList \mid Var\ VarList

ProcList

Proc | Proc ProcList

Globals

system IdList ; OpHide | OpHide system IdList ;

\rightarrow

Channel

chan IdList;

\rightarrow

Var

Type IdList:

Proc

process Id { ProcBody }

Id | Id , IdList

IdList

OpHide 1

\epsilon | hide IdList;

ProcBody

\rightarrow StateDecls TransDecls

state IdList; init Id; | state IdList; init Id; final Id;

StateDecls

\rightarrow

Transdecls

trans TransList ;

\rightarrow

TransList

Trans | Trans , TransList

\rightarrow

Trans

Id -> Id { OpGuard OpSync OpAssign }

\rightarrow

OpGuard

\epsilon \mid \mathsf{guard} \ GuardList;

\epsilon \mid Id! \mid Id ?

OpSync

\rightarrow

\rightarrow \epsilon \mid assign AssignList;

OpAssign

GuardList

\rightarrow

Guard \mid Guard , GuardList

Assign | Assign , AssignList

AssignList

\rightarrow

Type

clock | int | ...

Guard

ClockGuard | IntGuard | . . .

ClockAssign | IntAssign | . . .

Assign

\rightarrow

ClockGuard

Id RelOp Nat

\rightarrow

Id RelOp Int

IntGuard

\rightarrow

ClockAssign

Id := Nat

\rightarrow

IntAssign

Id := IntExpr

Int * Id + Nat \mid Int * Id - Nat \mid Id + Nat \mid Id - Nat \mid Id \mid Int

IntExpr

\rightarrow

RelOp

<= | >= | ==

Id

Alpha | Id AlphaNum

\rightarrow

Nat

\rightarrow Num | Num Nat

Nat | - Nat

Int

\rightarrow

Alpha

A | ... | Z | a | ... | z

Num

\rightarrow

0 | ... | 9

AlphaNum

Alpha | Num | _

```

Table 5.1: Context free grammar for the textual description language.

## 5.1.2 Textual Description Language

### The language

The textual description language is designed to be a simple textual representation of networks of timed automata. It also serves as a simple programming language for Timed Automata.

The language is defined by the context free grammar given in table 5.1.

## 5.1.3 Property Description Language

### The Language

The logic used to describe properties, in the tool, is a simple logic, to specify properties such as "Can some state be reached from the initial state?" or "Can we be sure that some state is not reachable from the initial state?".

The syntax of the property description language is defined by the context free grammar given in table 5.2

```

TopProp

Prop | not Prop

Prop

E<> StateProp | A [] StateProp

StateProp

AtomicProp | not StateProp | ( StateProp ) | StateProp or StateProp

| StateProp and StateProp | StateProp imply StateProp

AtomicProp

Id . Id | Id . * | Id RelOp Nat

RelOp

<= | >= | ==

Alpha | Id AlphaNum

Id

Nat

Num | Num Nat

Alpha

A | ... | Z | a | ... | z

Num

\rightarrow

0 | ... | 9

Alpha | Num | _

AlphaNum

```

Table 5.2: Context free grammar describing the property description language

### Parsing of the Logic

The properties are parsed using a parser generated using Flex and Bison, the wildcards are expanded, and an expression tree is built.

Before we can deliver the properties to the verifier they have to be transformed to disjunctive normal form. That is done automatically in a very naïve way, following the transformation-rules in table 5.3. Atomic propositions are either propositions telling that one process is in a specified state (e.g.  $P_1.S_1$ ), or simple constraints on the variables or clocks (e.g.  $c_1 \le 5$ ).

After the transformation, we will have an expression, either of the form  $\exists \Diamond P$ , or of the form  $\neg \exists \Diamond P$ , where P is a disjunct of conjuncted atomic properties (i.e. P has the form  $(a_{1,1} \land \ldots \land a_{1,n}) \lor \ldots \lor (a_{m,1} \land \ldots \land a_{m,q})$ .  $a_{i,j}$  are atomic propositions.).

#### Verifying Properties

Given a property in the form  $A_1 \vee \cdots \vee A_n$ , each  $A_i$  is used to build a symbolic final state for the system. Those states are then delivered, one by one, to the verifier, until a reachable one is found, or until they all have been tested.

If one of the final states built are reachable we can stop our verification process, since we now have an example (in case of a  $\exists \Diamond P$  property) or a counter-example (in case of a  $\neg \exists \Diamond P$  property).

```

Ρ

Nf(P)

if P is atomic

Nf(\neg P)

\neg P

if P is atomic

Nf(\neg(\neg P))

= Nf(P)

Nf(\neg(P_1 \wedge P_2))

= Nf(\neg P_1) \vee Nf(\neg P_2)

Nf(\neg(P_1 \lor P_2))

= Nf(\neg P_1 \wedge \neg P_2)

Nf(P_1 \vee P_2)

= Nf(P_1) \vee Nf(P_2)

Nf((P_1 \vee P_2) \wedge (P_3 \vee P_4)) = Nf(P_1 \wedge P_3) \vee Nf(P_1 \wedge P_4) \vee Nf(P_2 \wedge P_3) \vee Nf(P_2 \wedge P_4)

Nf(P_1 \wedge (P_2 \vee P_3))

= Nf(P_1 \wedge P_2) \vee Nf(P_1 \wedge P_3)

Nf((P_1 \vee P_2) \wedge P_3)

= Nf(P_1 \wedge P_3) \vee Nf(P_2 \wedge P_3)

Nf(P_1 \wedge P_2)

= Nf(Nf(P_1) \wedge Nf(P_2))

If none of the rules above

are applicable

Nf(\exists \Diamond P)

\exists \Diamond Nf(P)

Nf(\forall \Box P)

\neg \exists \Diamond Nf(\neg P)

```

Table 5.3: Transformation-rules for Transforming Expressions to Disjunctive Normal Form

## 5.2 The Constraint Solvers

## 5.2.1 The Clock Constraint Solver

### Representation

A region is a constraint system describing all values that are allowed for the clocks in the system. To represent regions, we only need two types of constraints:  $l_i \leq x_i \leq u_i$  and  $l_{i,j} \leq x_i - x_j \leq u_{i,j}$ .  $x_i$  and  $x_j$  are clocks,  $l_i, u_i, l_{i,j}$  and  $u_{i,j}$  are integer constants. No other form of clock constraints can occur. The first thing we notice is that we don't need  $l_{i,j}$ . They can be removed since  $l_{i,j} = -u_{j,i}$ . If the system has n clocks the indices i and j will range from 1 to n. We can represent the constraints in a  $n \times n$ -matrix containing the upper bounds and a n-dimensional vector containing the lower bounds. The matrix element (i,j) contains  $u_{i,j}$ , the upper bound for  $x_i - x_j$  when  $i \neq j$ , and the ith element of the vector contains  $l_i$ , the lower bound for  $x_i$ . We use the diagonal elements (i,i) to store  $u_i$ , the upper bound for  $x_i$ .

However, there's a more uniform representation which makes algorithm design and implementation much simpler. Instead of using a  $n \times n$ -matrix we will use a  $(n+1) \times (n+1)$ -matrix. The indices i and j now ranges from 0 to n and the extra elements  $(i,0) = u_{i,0}$  now contains the upper bounds for  $x_i - 0 = x_i$ . By analogy we let the elements  $(0,j) = u_{0,j}$  contain the upper bounds for  $0 - x_j = -x_j$ . Now we don't need the n-dimensional vector any longer. The reason is that  $u_{0,i} = -l_i$  Now we're able to write all clock constraint in a uniform way, namely on the form  $x_i - x_j \le u_{i,j}$  where i and j ranges from 0 to n and  $i \ne j$ , keeping in mind that  $x_0 = 0$  and the system still has n clocks  $x_1$  through  $x_n$ .

Before we can close the discussion of representation there's one thing that remains to be solved. How do we represent the fact that there is no restriction for a given clock or clock difference. This must be done by reserving a special value to put in the matrix. In order to choose an appropriate value we have to find what values are allowed for  $u_{i,j}$ . Clock values are always non-negative so  $u_{0,j} \leq 0$  and  $u_{i,0} \geq 0$ . The other bounds  $u_{i,j}$ ,  $i = 1, ..., n, j = 1, ..., n, i \neq j$  have no such restrictions, they can range from  $-\infty$  to  $+\infty$ . We choose a large integer, much larger than the maximum upper bound to be used, and let it represent infinity. We denote this integer INF and treat it like  $\infty$  so that  $INF \pm n = INF$  for any integer n. We will use -INF as  $-\infty$ .

Note that the matrix representation contains some redundancy because we don't use the matrix

diagonal. According to our interpretation these elements shall contain the upper bounds for  $x_i - x_i = 0$  which clearly is zero; it even holds for our definition of  $x_0$ . Despite of that, we store them to make the algorithms a bit easier and faster. If not storing them, we will save some memory but lose some time due to extra tests needed when reading and writing matrix elements. These elements will also be used to indicate some properties about the constraint systems. The problem now is to find algorithms that given matrices of the type described above return matrices of the same type corresponding to constraint systems describing the clock assignments after the clock constraint operations in chapter 3.

### Conjuncting Guards

One operation that we'll need quite frequently is to conjunct a clock guard and determine if the constraint system still is consistent, that is if the constraints contain no contradictions. A contradiction arise when a lower bound of a clock or clock difference is greater than the corresponding upper bound. A consistent constraint system must satisfy  $u_{i,j} + u_{j,i} \geq 0$  for all i and j. This condition can be intuitively understood if one observe that the quantity  $u_{i,j} + u_{j,i}$  is the length of the allowed interval for  $x_i - x_j$  which is greater than or equal to zero in a consistent constraint system. The guards allowed in the system are of the forms  $x_i \geq l_i$  and  $x_i \leq u_i$

or written in the form developed in the previous subsection  $-x_i \leq -l_i = u_{0,i}, x_i \leq u_i = u_{i,0}$ . There is a simple way to conjunct such a guard. Assume that we want to conjunct a guard of the form  $l \leq x_i \leq u$  and let  $u'_{i,0}$  and  $u'_{0,i}$  be the current value of  $u_{i,0}$  and  $u_{0,i}$  respectively. Let min(x,y) denote the minimum of the two integers x and y. The idea is to set  $u_{i,0} = min(u'_{i,0}, u)$  and  $u_{0,i} = min(u'_{0,i}, -l)$ . This will of course yield a correct constraint system but it can cause some problems as we'll see in the examples below. We will use this method anyway because a guard can be conjuncted in constant time. After the conjunction the constraint system can be transformed to a representation that doesn't cause us any problems. The next example will show what we mean when we talk about different representations for a given constraint system.

In the following examples we will not use the representation of constraints that is used in the implementation. Instead we will use a more familiar representation which is easier to read.

**Example 1** Assume that we want to conjunct the guard  $0 \le x_2 \le 2$  to the constraint system

$$0 \le x_1 \le 4, 1 \le x_2 \le 3, x_1 - x_2 \le 0, x_2 - x_1 \le 0$$

After the conjunction the constraint system has changed to

$$0 < x_1 < 4, 1 < x_2 < 2, x_1 - x_2 < 0, x_2 - x_1 < 0 \tag{5.1}$$

This representation does not have the lowest possible upper bounds but it is correct. The last two constraints in 5.1 are simplified to  $x_1 = x_2$  and the constraint system can be written as

$$1 < x_1 < 2, 1 < x_2 < 2, x_1 - x_2 < 0, x_2 - x_1 < 0$$

(5.2)

The constraint systems 5.1 and 5.2 are in fact equivalent but the representation in 5.2 is much more useful and does not cause the problems associated with the representation in 5.1.

If we add an inconsistent guard we will definitely get an inconsistent constraint system but that can happen even if the conjuncted guard is consistent. In order to apply the syntactic definition of inconsistency we must have the constraint system represented as in 5.2 and not as in 5.1.

Let  $r_1$  be the constraint system in the example above after the guard conjunction. We will call 5.2 the closed representation of  $r_1$  and 5.1 an open representation of  $r_1$ . A closed constraint system is a representation where all upper bounds are as low as possible still containing the same set of solutions. A solution is a vector that satisfies the constraint system, in this case a clock assignment.

**Example 2** Let us now conjunct the guard  $x_1 = 3$  to  $r_1$ . If we use the representation in 5.1 we get

$$3 < x_1 < 3, 1 < x_2 < 2, x_1 - x_2 < 0, x_2 - x_1 < 0$$

(5.3)

The representation in 5.2 yields

$$3 < x_1 < 2, 1 < x_2 < 2, x_1 - x_2 < 0, x_2 - x_1 < -1$$

(5.4)

One immediately discovers the inconsistency in 5.4 but it's much more difficult to detect the inconsistency in 5.3.

Another problem arises when we look at relationships between regions.

**Example 3** Let  $r_1$  be as before and define  $r_2$  to be the region

$$0 \le x_1 \le 5, 1 \le x_2 \le 2, x_1 - x_2 \le 0, x_2 - x_1 \le 0$$

If we apply the relation algorithm to check implication between constraint systems, described later, on  $r_2$  and 5.1 we will find that the solution set of 5.1 is included in  $r_2$ . If we close  $r_2$  and apply the algorithm on 5.1 and  $r_2$  we see that the solution set of  $r_2$  is included in 5.1. If we finally apply the algorithm on 5.2 and the closed representation of  $r_2$  we will get the correct answer,  $r_1$  and  $r_2$  are equivalent.

**Definition 16** Two constraint systems are equivalent if they have the same set of solutions. □

The property that a constraint system is closed is very important for our further work. We postpone the treatment of how to check for inconsistency of a region for a while and first discuss how to find the closed representation of a constraint system. We also save the discussion of the relation algorithm until later.

## Closing the Constraint System

As mentioned in the previous subsection the concept of closed constraint systems is very important. We therefore need an efficient algorithm to close a region. As noticed we also talked about "an open representation" and "the closed representation" of a constraint system. This indicates that there are many open representations for a given constraint system but only one closed. In fact, there are infinitely many open representations because all upper bounds  $u_{i,0}$  and some upper bounds  $u_{i,j}$  have the property that if one adds an arbitrary positive integer, the constraint system remains consistent and we get a new open representation of the same region.

Proposition 1 The closed representation of a constraint system is unique.

**Proof** To prove that the closed representation is unique we assume that we have two different closed representations, with upper bounds  $u_{i,j}$  and  $u'_{i,j}$ , of a given region. If the representations are different there must exist at least one i and j for which  $u_{i,j} \neq u'_{i,j}$ . In a closed representation however each upper bound shall be as low as possible so only the minimum of these two upper bounds belongs to the closed representation, the other belongs to an open. To avoid the contradiction that one representation can be both open and closed we must conclude that our assumption made above was wrong and hence the closed representation is unique.

It is now possible to give an alternative definition of what we mean when we say that two constraint systems are equivalent.

**Definition 17** Two constraint systems are equivalent if they have the same closed representation, that is if all corresponding upper bounds are equal.

When finding the lowest possible upper bound in a constraint system many candidates of upper bounds must be examined. For example in a system with only three clocks, finding the correct value of  $u_{1,0}$  would require us to compare it to each of the candidates  $u_{1,2}+u_{2,0}$ ,  $u_{1,3}+u_{3,0}$ ,  $u_{1,2}+u_{2,3}+u_{3,0}$  and  $u_{1,3}+u_{3,2}+u_{2,0}$ . These bounds may in turn depend on other bounds not yet computed which require us to determine in which order to compute the bounds if such a partial ordering exists. There is no efficient way to do that.

The solution is to model the constraint system as a weighted graph as described in [YL93]. We have one node for each clock, including  $x_0$ , and an edge from node i to node j labeled by  $u_{i,j}$ . That's the main reason for why we chose the representation as a matrix with upper bounds. It is in fact a way to represent a weighted graph. Another way of representing the region or a weighted graph is as a linked list. However our regions often consist of too many constraints to use the list representation. The different candidates of upper bounds  $u_{i,j}$  now correspond to sums of weights along paths between node i and j. The upper bounds in the closed representation are the shortest paths, the paths with the lowest sum of weights. If we store all shortest paths in the matrix we get a matrix corresponding to the closed representation of the original region.

**Theorem 1** The upper bounds  $u_{i,j}$  corresponding to the shortest paths from node i to node j are the upper bounds of the closed representation of the original constraint system.

Before we prove this theorem we need a lemma.

**Lemma 1** In a constraint system with upper bounds  $u_{i,j}$  obtained from the shortest path algorithm a clock assignment  $\vec{x}$  with components  $x_i = u_{i,0}$  and  $x_i = u_{0,i}$  are solutions.

**Proof** Let  $x_i = u_{i,0}$ . Of course  $u_{i,0} \le u_{i,0}$  and  $-u_{i,0} \le u_{0,i}$ . What remains to prove is that  $x_i - x_j = u_{i,0} - u_{j,0} \le u_{i,j}$ . This follows directly because the upper bounds are the shortest paths and hence satisfies

$$u_{i,0} \le u_{i,j} + u_{j,0} \Leftrightarrow u_{i,0} - u_{j,0} \le u_{i,j}$$

The second part of the proof, to show that  $x_i = -u_{0,i}$  also is a solution to the constraint system, is similar and is not shown here.

We are now ready to give the proof for the theorem.

**Proof** To prove that the matrix containing all shortest paths represents the closed original constraint system we must prove two things: We must prove that the obtained constraint system is equivalent to the original one and that the obtained upper bounds are as low as possible.

The first thing is obvious because we only examine the paths in the graph, or different combinations of constraints, to discover the one with smallest sum of weights. We therefor don't lose any solutions not present in the original constraint system, or add any extra solutions not present there. Hence the set of solutions is preserved.

To prove that the shortest path really corresponds to the upper bound of the closed representation, the constraint system has the tightest possible bounds, is more difficult: Assume that we have a clock assignment  $\vec{x}$  satisfying  $x_i - x_j = u_{i,j}$  without any special restrictions on i and j except that they are less than or equal to n. If this assignment is a solution we know that the constraint system is closed, because if we lower  $u_{i,j}$  we will lose that solution.

We can assume that the constraint system is consistent and we select a  $x_i$  so that  $x_i \leq u_{i,0}, -x_i \leq u_{0,i}$ . If  $x_j = x_i - u_{i,j}$  satisfies the constraint system we are ready. To prove that  $x_j \leq u_{j,0}$  we observe that

$$x_j = x_i - u_{i,j} \le u_{i,0} - u_{i,j} \le u_{i,j} + u_{j,0} - u_{i,j} = u_{j,0}$$

The inequality  $u_{i,0} \leq u_{i,j} + u_{j,0}$  is a direct consequence of the shortest path algorithm. It simply says that since we have all shortest paths we know that the path direct from node i to node 0 must be shorter than the path from node i to node 0 via node j.

To prove that  $-x_j \leq u_{0,j}$  requires a little trick: The proof idea is to choose a  $x_i$  that satisfies the constraint system and then show that  $x_j$  also does so. Let us choose  $x_i = u_{i,0}$  which according to the lemma satisfies the constraint system. We can now easily show that

$$-x_j = u_{i,j} - x_i \le u_{i,0} + u_{0,j} - x_i = u_{i,0} + u_{0,j} - u_{i,0} = u_{0,j}$$

Note that the inequality  $u_{i,j} \leq u_{i,0} + u_{0,j}$  is a direct consequence of the shortest path algorithm. This completes the proof that the shortest path algorithm gives a closed constraint system.

**Corollary 1** When a constraint system is modeled as a graph which is processed by the shortest-path algorithm, consistency is preserved.

There's an efficient way of finding all shortest paths for a weighted graph represented as a matrix. We will use Floyd's algorithm [Flo62]<sup>2</sup>. The matrix first contains weights telling us the lengths of the paths from node i to node j without visiting any other node. We now compare these paths from node i to node j with the paths we get if we are allowed to visit node 0 when moving from node i to node j and if we found any shorter path we store that one instead. In that way the matrix element (i, j) always contains the best path from node i to node j encountered so far. We repeat the procedure but now we're allowed to move from node i to j via node 1 and so on. We continue in this way, visiting a node with a higher index each time, until the procedure has been repeated for all nodes and the algorithm terminates with a matrix containing all shortest paths and hence a closed representation of the constraint system. We show some pseudo-code below.

**Algorithm 3** • For every node k do

- For every node i do

- \* For every node j do

<sup>&</sup>lt;sup>2</sup>Dijkstra's algorithm will be more inefficient because the graphs are often very dense.

$$\cdot Set u_{i,j} = min(u_{i,j}, u_{i,k} + u_{k,j})$$

If the system has n clocks we have n+1 nodes in the graph and therefore  $(n+1)^2$  paths yielding an algorithm with time complexity  $O(n^3)$ . But there is still one remaining problem to solve.

There's one requirement that the graph must satisfy when using Floyd's algorithm, or any shortest-path algorithm, to obtain a correct answer. The graph must not contain cycles with a negative sum of weights. If it does, the concept of "shortest path" will no longer have any meaningful interpretation since one can cycle around making a path arbitrarily short. The algorithm will still terminate even if the graph contains such cycles because it's totally deterministic but the result will be useless. How do we know that our weighted graph, modeling the constraint system, satisfies this property?

In order to answer this question we look at the sum of weights along the shortest cycle from a node i back to itself because if that cycle has a non-negative sum of weights all other cycles have that too. This cycle is easy to find after the shortest-path algorithm has been applied. Now when the matrix contains the shortest paths the shortest cycle from node i and back to itself must be one from node i, to another node j and directly back to i again because if there is a shorter one going via node k from i to node j then the path from node i to node j, stored in the matrix, would not be the shortest which leads to a contradiction. The sum of weights along these cycles are given by  $u_{i,j} + u_{j,i}$  so the shortest such cycle has a sum of weights which is

$$min_{i,j}(u_{i,j} + u_{j,i}) = min_i(u_{i,i})$$

We have no cycles with a negative sum of weights if this quantity is greater than or equal to zero and that's precisely the condition that must hold for consistent constraint systems. According to the corollary above, consistency is preserved, So we can look in the matrix containing the shortest paths and draw conclusions about the original constraint system. This shows us that a graph, modeling a consistent constraint system contains no negative cycles and hence satisfies the condition required. It doesn't matter if the algorithm gives an incorrect answer for inconsistent constraint systems.

We have almost derived an algorithm to determine if a given constraint system is consistent or not and we explain it in detail, together with some improvements in the next subsection.

#### Checking for Consistency

This subsection will be a very short one since most of the work has already been done in the previous subsection. However the algorithm is placed in a separate subsection for readability. In an earlier subsection we came to the conclusion that a necessary condition for a closed constraint system to be consistent is  $u_{i,j} + u_{j,i} \ge 0$ . This property shall hold for all i and j. This condition is also sufficient because no other kind of contradictions can occur. This condition only holds for closed constraint systems. This yields an algorithm to check consistency for constraint systems with time complexity  $O(n \ 2)$  where n is the number of clocks in the system. However, it is enough to look at  $min_{i,j}(u_{i,j} + u_{j,i}) = min_i(u_{i,i})$  and see if it is greater than or equal to zero or not. This yields an algorithm with complexity O(n).

However, we can do much better in this case because we only get inconsistencies after guard conjunctions. This implies that if the constraint system is inconsistent there exists at least one k such that  $u_{0,k} + u_{k,0} < 0$ . After the application of the closing algorithm we know that  $u_{0,0} = \min_k (u_{0,k} + u_{k,0})$  Hence, it's enough to examine  $u_{0,0}$  in order to determine consistency. We now have an algorithm with time complexity O(1).

To evaluate a clock guard with respect to a given global state, we do the following steps:

- 1. Conjunct the guard to the region in the global state.

- 2. Close the region.

- 3. Check if the resulting region is consistent. Return true if the constraint system is consistent, false otherwise.

The above is a description of a general evaluation procedure for evaluating clock guards and it is entirely composed of primitive operations, implemented and described above. It's not a precise description of the implementation used in the tool. When evaluating the guards belonging to a transition all of them must be satisfied. It's therefore a waste of time to do the last two steps after each conjunction. Even if we can save some guard conjunctions if we discover an inconsistency we must remember that the time of a guard conjunction is almost negligible compared to a close operation. Instead these two steps are done only once after all guard conjunctions. Here we clearly see a trade-off between generality and speed. Since this evaluation operation is done frequently during a verification, and the general evaluation procedure is easy to implement guided by the steps above, we determined that time was more important than generality in this case.

### The Weakest Precondition

The weakest precondition deals with what happens when time flows. Thus, we define the weakest precondition of a region r as the region containing all clock assignments which when time flows after some finite delay will lead to a clock assignment in r. We denote that region r' so that r' = wp(r). This can be expressed mathematically as if  $\vec{z} \in r'$  and  $\vec{x} \in r$  then  $\vec{x} = \vec{z} + \vec{d}$  where  $\vec{z}$  and  $\vec{x}$  are clock assignments with components  $z_i$  and  $x_i$  respectively. The vector  $\vec{d}$ , with components  $d_i$ , is the delay required for the clock assignment  $\vec{z}$  to lead to clock assignment  $\vec{x}$ . Since all clock rates are the same we have  $d_i = d$  and r' consists of exactly those  $z_i$  for which  $z_i + d = x_i$  for some finite delay d, d = 0 is allowed. How do we find the constraint system describing r'?

Assume that r' is a constraint system of the form  $x_i - x_j \le u'_{i,j}$  and r is on the form  $x_i - x_j \le u_{i,j}$ . Intuitively we want to find as low lower bounds for the clocks as possible <sup>3</sup>. This can be obtained by setting  $u'_{0,i} = 0$  and then close r' to get the correct lower bounds because no lower bound can be less than zero. Before we do that however we must ensure that the clocks don't drift away. We must remember that all clock rates are the same.

**Example 4** If we have an assignment  $x_1 = 2$ ,  $x_2 = 4$  then all previous assignments  $\vec{z} \in r'$  leading to that assignment must have  $z_1 - z_2 = -2$ . The other constraints describing r' is  $0 \le z_1 \le 2$ ,  $2 \le z_2 \le 4$ .

Note that if the previous value of  $u_{1,2}$  is less than -2 we must keep that one instead so what we actually say is that the maximum difference between  $z_i$  and  $z_j$  is the smallest of  $u_{i,j}$  and the difference between the maximum value of  $x_i$  and the minimum value of  $x_j$ ,  $u'_{i,j} = min(u_{i,j}, u_{i,0} + u_{0,j})$ . However, if r is closed we already have the correct values for  $u'_{i,j}$ ,  $u'_{i,j} = u_{i,j}$ .

**Algorithm 4** Let r be a closed constraint system of the form  $x_i - x_j \le u_{i,j}$  and r' = wp(r) of the form  $x_i - x_j \le u'_{i,j}$ . An open representation of r' can be obtained in the following way:

<sup>&</sup>lt;sup>3</sup>Because we relax the lower bounds the weakest precondition operation is sometimes called the down operation

- Set  $u'_{i,0} = u_{i,0}$  for all i.

- Set  $u'_{0,j} = u_{0,j}$  for all j.

- Set  $u'_{i,j} = u_{i,j}$  for all other pairs of i and j.

**Theorem 2** The constraint system obtained with the algorithm above is the weakest precondition of the original constraint system.

**Proof** In order to prove the above theorem we need to prove two things. We must prove that r' is big enough so that all  $\vec{x} \in r$  are reachable if some finite delay d is added to some  $\vec{z} \in r'$ . We must also prove that r' isn't too big so that each  $\vec{z} \in r'$  after some finite delay d leads to a clock assignment  $\vec{x} \in r$ .

The proof that r' is big enough is trivial: We can write all clock assignments  $\vec{z}$  that after some delay  $\vec{d}$  will lead to a clock assignment  $\vec{x}$  as  $\vec{x} - \vec{d}$ . For all d we have

$$x_i - x_j = (x_i - d) - (x_j - d) = z_i - z_j \le u'_{i,j} = u_{i,j}$$

Because  $d \ge 0$  we must also have

$$-z_i = d - x_i \le u'_{0,i} \Rightarrow -x_i \le u'_{0,i}$$

We also know that  $x_i \leq u_{i,0} = u'_{i,0}$ .

Because  $z_i$  is a clock value and hence is non-negative we observe that  $d \leq \min_i(x_i)$ . These observations are the complete proof that r' is big enough.

To prove that r' isn't too big is a little bit harder. We start with a clock assignment  $\vec{z} \in r'$  and try to find a  $\vec{d}$  such that  $\vec{z} + \vec{d} = \vec{x} \in r$ . If we choose

$$d = min_i(u'_{i \mid 0} - z_i)$$

we'll get a valid d. Let's assume that this minimum occurs when i=1. This is no restriction because we can always renumber the clocks in that way. Because  $z_1 \leq u'_{1,0}$  we have  $d \geq 0$ . We also see that  $d \leq min_i(x_i)$  because  $z_i \geq 0$  and  $min_i(x_i) = min_i(z_i) + d$ . We also note that

$$(z_i - z)_j = (z_i + d) - (z_j + d) = x_i - x_j \le u'_{i,j} = u_{i,j}$$

We also get

$$x_i = z_i + d = z_i + u'_{1,0} - z_1 \le z_i + u'_{i,0} - z_i = u'_{i,0} = u_{i,0}$$

In order to prove that  $-x_i \leq u_{0,i}$  we use the following trick: We rewrite  $x_i$  as  $x_i - x_1 + x_1$ . According to our choice of d this can be written as

$$x_i = (x_i - d) - (x_1 - d) + x_1 = z_i - z_1 + u'_{1,0}$$

If we rely on the assumption that r is closed we can show that

$$-x_i = z_1 - z_i - u'_{1,0} \le u'_{1,0} + u'_{0,i} - u'_{1,0} = u'_{0,i}$$

This completes the proof that our proposed algorithm is correct.

<sup>&</sup>lt;sup>4</sup> Note that no delay is added to  $x_0$  so in the proves that follows we must treat all cases where i = 0 or j = 0 separately

Another way of finding the weakest precondition of a region is to view it as a linear programming problem, often abbreviated lp-problem <sup>5</sup>. We want to find the lowest possible values for the lower bounds  $-u'_{0,i}$  and these are the lowest values that the clocks  $x_i$  can have, we can find them if we minimize  $\sum_i x_i$  subject to the constraints  $x_i \leq u'_{i,0}, x_i - x_j \leq u'_{i,j}$ . Since the clocks are nonnegative the sum will assume its minimum when every  $x_i$  is as small as it can be. Geometrically one can visualize the region as a convex polytope in  $\mathbf{R}^{+n}$  and the theory for linear programming states that the optimal solution always is a corner point of the polytope. We can only accept integer solutions because  $u'_{0,i}$  must be an integer. We know that the corner points of this polytope have integer coordinates because  $u'_{i,0}$  and  $u'_{i,j}$  are all integers so we don't need branch-and-bound or cutting-plane methods.

One of the most common methods for solving such problems is the simplex method. The time performance of this method is in average case proportional to  $\rho m^2 n$  where n is the number of variables, m is the number of constraints and  $\rho$  is the matrix density. The matrix used most conveniently with the simplex method has a structure different from the matrix representation used so far. Since there are  $n^2$  constraints, we need to introduce  $n^2$  slack variables  $n^6$ . The simplex method require an initial solution to start with and if some  $u'_{i,j}$  is negative, which is very likely to be the case, one must solve an extra lp-problem to get that initial solution. This problem is solved by use of artificial variables and there will be at most  $\frac{n(n-1)}{2}$  of these in a consistent constraint system. This fact holds because  $u_{i,j} + u_{j,i} \geq 0$  and if  $u_{i,j} < 0$  we know that  $u_{j,i} > 0$ . The time complexity is  $O(n^6)$  because  $m = n^2$  and there is merely  $n^2$  variables. It will take some extra time to build the new matrix as well because the representation required by the simplex method would make it difficult to for example close a constraint system in an efficient way. Adapting the simplex method to our representation would slow it down even more.